The Dissertation Committee for Kimble Derek Houck certifies that this is the approved version of the following dissertation:

# Hardware Implementation of Inference in Deep Neural Networks

Committee:

Risto Miikkulainen, Supervisor

Dana Ballard

Don Fussell

Thibaud Taillefumier

# Hardware Implementation of Inference in Deep Neural Networks

by

# Kimble Derek Houck

#### Dissertation

Presented to the Faculty of the Graduate School of the University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

# **Doctor of Philosophy**

The University of Texas at Austin May 2022

# Acknowledgments

First of all I'd like to thank the team I was a part of at Centaur Technology that designed an actual SoC implementation of the hardware design paradigm described in this document, including Glenn Henry for coming up with the original idea for the design (and recruiting me and supporting my continuing my PhD work while working for Centaur). Additionally I'd like to thank my colleagues Jim Donahue, Terry Parks, Kyle O'Brien, Parviz Palangpour, Tyler Walker, Benjamin Seroussi, Bryce Arden, Scott Gardner, Scott Petersen, Jonathan Johnson, Mark Ebersole, Anna Slobadova, Patrick Roberts, Doug Reed, Paul Zucknick and everyone else at Centaur who helped with the hardware design or encouraged my work towards my dissertation.

Second, I'd like to thank my advisor, Risto Miikkulainen, and my committee members Dana Ballard, Don Fussell, and Thibaud Taillefumier for their patience and encouragement along this journey. Additionally, I'd like to thank my masters thesis advisor, Andrew Fagg, for encouraging me to apply to UT Austin in the first place.

Finally, I'd like to thank my family and friends for all their support and encouragement, and especially my parents for their financial support.

### Abstract

# Hardware Implementation of Inference in Deep Neural Networks

by

Kimble Derek Houck, Ph.D. The University of Texas at Austin, 2022 Supervisor: Risto Miikkulainen

Deep learning neural network algorithms, including convolutional and recurrent networks, have risen to popularity in recent years. Along with this popularity has come a wide range of implementations that optimize the performance of these algorithms on existing hardware, including GPU architectures and with modern x86 CPU SIMD capabilities. Likewise, effort has been put into developing hardware specifically for running these algorithms, either focusing on specific algorithms or on a range of building block operations common to many deep learning variations. While some of these architectures, have large power requirements and are generally designed to run in a datacenter environment, hardware architectures that are designed to run most deep learning well while being small, low cost and/or power are also important for applications where these are limiting factors.

In this work I will describe the implementation of both convolutional and recurrent network layer types on such a novel hardware architecture. This novel ultra-wide SIMD architecture is built around a ring of simple data movement and register units that feed simple arithmetic units, attached accumulator registers and post-processing units. Unlike many other architecture designs however, this class of hardware designs posses few methods for efficiently rearranging data over even moderate distances in memory but rather relies on shifting data between adjacent or nearby data units in the ring. Thus, neural network implementations that take the geometry of the inputs into account as much as possible are needed. I present one such implementation,  $M^3 in M^2 V$ , and show that it allows such simple hardware architectures to be efficiently used for neural network inference, analyzing both it's performance on the described novel architecture and the very different AVX-512 SIMD architecture.

Furthermore, I show the applicability of recurrent network architectures to a novel domain; the decoding of information encoded in the electrical spiking activity observed from ensembles of neurons. By comparing the ability of a classifier to infer different pieces of information from the data and/or comparing classifiers trained using different methods of transforming the observed activity into feature vectors inferences can be made about what information is encoded in the neural signal, and how. By showing that deep learning classifiers can perform useful classification on such a dataset, possibly with less parameter tuning than other classifiers, I show that such tools can contribute to increasing scientific understanding of the brain. Furthermore, for future applications for decoding neural signals such as the control of prosthetic devices, the ability to run the decoding algorithms on relatively low power hardware would be highly advantageous.

# Table of Contents

| Chapte | er 1 In                                           | troduction                                                    | 1  |  |

|--------|---------------------------------------------------|---------------------------------------------------------------|----|--|

| 1.1    | Motiv                                             | ation                                                         | 1  |  |

| 1.2    | Proposed approach                                 |                                                               |    |  |

| 1.3    | 8 Real world application: decoding neural signals |                                                               |    |  |

| 1.4    | Guide                                             | to the reader                                                 | 4  |  |

| Chapte | er 2 Ba                                           | ackground                                                     | 6  |  |

| 2.1    | Neura                                             | l nets and deep learning                                      | 6  |  |

|        | 2.1.1                                             | Deep learning and the resurgence of Neural Network Algorithms | 6  |  |

| 2.2    | Comp                                              | uting hardware and deep learning                              | 11 |  |

|        | 2.2.1                                             | Implementation of Convolutional Networks across Hardware      |    |  |

|        |                                                   | Architectures                                                 | 11 |  |

|        | 2.2.2                                             | x86 Implementations                                           | 11 |  |

|        | 2.2.3                                             | GPU implementations                                           | 13 |  |

|        | 2.2.4                                             | Custom and experimental hardware implementations              | 13 |  |

|        | 2.2.5                                             | TPUs                                                          | 14 |  |

| 2.3    | AVX-512 Overview                                  |                                                               |    |  |

|        | 2.3.1                                             | Changes from previous AVX instructions                        | 16 |  |

| 2.4    | Ultra-wide SIMD hardware description              |                                                               |    |  |

|        | 2.4.1                                             | New Ultra-wide SIMD Hardware                                  | 17 |  |

|        | 2.4.2                                             | Hardware and Instruction Set Architecture (ISA) Overview      | 17 |  |

|        | 2.4.3                                             | Motivation for Ultra-wide Paradigm                            | 19 |  |

| 2.5    | Machi                                             | Machine Learning and Decoding Neural Signals                  |    |  |

|        | 2.5.1                                             | Machine Learning Techniques for Neuroscience Timeseries Data  | 21 |  |

|        | 2.5.2                                             | Simple Classifiers                                            | 21 |  |

|        | 2.5.3                                             | Machine Learning                                              | 22 |  |

|        | 2.5.4                                             | Neural Network Algorithms                                     | 22 |  |

|        | 2.5.5                                             | Timeseries Algorithms for Neural Data                         | 23 |  |

|        |                                                   |                                                               |    |  |

# Chapter 3 Convolutional Network Computations on Ultra-wide SIMD Hardware

25

|                        | 3.1   | Insight                                              |                                                              |           |  |

|------------------------|-------|------------------------------------------------------|--------------------------------------------------------------|-----------|--|

| 3.2                    |       | Algorithm                                            |                                                              |           |  |

|                        |       | 3.2.1                                                | Layout of input data in cache memory                         | 27        |  |

|                        |       | 3.2.2                                                | Layout of weight values in cache memory                      | 29        |  |

|                        |       | 3.2.3                                                | Convolution Operation                                        | 30        |  |

|                        | 3.3   | Variations to accommodate new convolution algorithms |                                                              |           |  |

|                        |       | 3.3.1                                                | Depthwise Convolution                                        | 35        |  |

|                        |       | 3.3.2                                                | Strided Convolution                                          | 36        |  |

|                        |       | 3.3.3                                                | Dilated Convolution                                          | 39        |  |

|                        |       | 3.3.4                                                | Other convolution variants                                   | 40        |  |

|                        | 3.4   | Summ                                                 | ary of $M^3 in M^2 V Conv$ Convolution Algorithms            | 41        |  |

| Ch                     | apte  | er 4 Qi                                              | uantitative Analysis on Proposed Ultra-Wide SIMD Hard-       |           |  |

|                        | -     | wa                                                   | are                                                          | 42        |  |

|                        | 4.1   | Memo                                                 | ry Usage                                                     | 42        |  |

|                        |       | 4.1.1                                                | Effect of Network Parameters on Effecient Memory Usage       | 45        |  |

|                        |       | 4.1.2                                                | Summary of Memory Usage Analysis                             | 45        |  |

|                        | 4.2   | Comp                                                 | utational Efficiency                                         | 46        |  |

|                        |       | 4.2.1                                                | Effect of Network Parameters on Computational Efficiency     | 46        |  |

|                        |       | 4.2.2                                                | Effect of Data Movement on Computational Efficiency          | 47        |  |

|                        |       | 4.2.3                                                | Effect of Convolution Variations of Computational Efficiency | 48        |  |

|                        | 4.3   | Perfor                                               | mace Conclusions                                             | 49        |  |

| $\mathbf{C}\mathbf{h}$ | apte  | er 5 In                                              | plementation on Existing AVX-512 Hardware                    | 51        |  |

|                        | 5.1   |                                                      | se: Prove algorithm generalizes to other wide hardware       | 51        |  |

|                        | 5.2   | Implei                                               | mentation                                                    | 52        |  |

|                        | 5.3   |                                                      | utational Efficiency                                         | 54        |  |

|                        | 5.4   | Register/memory usage                                |                                                              |           |  |

|                        | 5.5   |                                                      | l Run                                                        |           |  |

|                        | 5.6   | Lessor                                               | ns Learned                                                   | 56        |  |

| $\mathbf{C}\mathbf{h}$ | apte  | er 6 G                                               | ated Recurrent Network Computations on Ultra-wide            |           |  |

| - 11                   | ~P // |                                                      | MD Hardware                                                  | <b>58</b> |  |

|                        | 6.1   |                                                      |                                                              | 58        |  |

| 6.2                                              | LSTM Algorithm                                                      | 59 |  |  |  |

|--------------------------------------------------|---------------------------------------------------------------------|----|--|--|--|

| 6.3                                              | Hybrid Recurrent-Convolution: Quasi Recurrent Neural Networks       | 60 |  |  |  |

| Chapte                                           | Chapter 7 Proposed Application in Decoding Neural Signals           |    |  |  |  |

| 7.1                                              | Problem Definition                                                  | 62 |  |  |  |

|                                                  | 7.1.1 Predicting Task Relevant Stimulus Frequency Change from Rat   |    |  |  |  |

|                                                  | Auditory Cortex Spike Data                                          | 63 |  |  |  |

| 7.2                                              | Method for augmenting training data for neural spike datasets       | 65 |  |  |  |

| 7.3                                              | 3 Recurrent networks for decoding auditory cortex data              |    |  |  |  |

| 7.4                                              | Conclusion                                                          |    |  |  |  |

| Chapte                                           | er 8 Discussion and Future Work                                     | 73 |  |  |  |

| 8.1                                              | Exploring Performance on Other Hardware Types                       | 73 |  |  |  |

| 8.2                                              | Other domains - Cybersecurity applications such as anomaly and mal- |    |  |  |  |

|                                                  | ware detection                                                      | 73 |  |  |  |

|                                                  | 8.2.1 Source and Binary Code Analysis                               | 74 |  |  |  |

|                                                  | 8.2.2 Intrusion and Anomaly Detection                               | 74 |  |  |  |

|                                                  | 8.2.3 IoT and Edge Security                                         | 76 |  |  |  |

| Chapte                                           | er 9 Conclusion                                                     | 77 |  |  |  |

| 9.1                                              | Contributions                                                       | 77 |  |  |  |

| 9.2                                              | Broader Impact                                                      | 78 |  |  |  |

| 9.3                                              | Next Steps: Continued Development                                   | 79 |  |  |  |

| Bibliog                                          | graphy                                                              | 82 |  |  |  |

| Chapte                                           | er AAXV-512 Convolution Algorithm C Code (with intrinsics)          | 88 |  |  |  |

| Chapter BAXV-512 Convolution Algorithm C Run Log |                                                                     |    |  |  |  |

#### Chapter 1

### Introduction

This dissertation presents a novel algorithm for performing convolution operations like those used in deep learning networks, on a proposed class of massively parallel, yet relatively simple, hardware architectures. Specifically, these architectures sacrifice flexibility in the ability to rearrange data in the SIMD vectors in exchange for the ability to support SIMD widths in the thousands of bytes. My algorithm facilitates this trade-off by performing the convolution in a geometry aware manner that eliminates the need for many complex data movement patterns, thus allowing it to be run on hardware that provides limited data movement capabilities.

### 1.1 Motivation

The rise in popularity of deep learning has spawned the development of new tools and hardware capabilities to run the algorithms more efficiently. This includes methods of computing deep network layers that take advantage of operations that have already been optimized on various architectures using standard compute libraries such as BLAS (Chellapilla et al., 2006, Mathieu et al., 2013). It also includes higher level software packages that separate the selections of these optimized methods and hardware on which to run them from the design of the deep networks themselves (Dieleman et al., 2015, Al-Rfou et al., 2016). On the hardware side new architectures have even been proposed, such as those by Chen et al. (2014), Qadeer et al. (2015), or Liu et al. (2016), which provide varying levels of generalizability to different and potentially novel deep-learning architectures. Some of these architectures have large power requirements and are generally designed to run in a datacenter environment.

However, hardware architectures that are designed to run most deep learning architectures well while being small, low cost and/or power are important for applications where these are limiting factors. One obvious route for supporting deep learning algorithms with such hardware is expanding the on-chip parallelism while keeping the circuitry as small and simple as possible. This can be achieved either by (1) increasing the number of cores or arithmetic units on the chip, or by (2) increasing the number on simultaneous arithmetic operations that each core can perform at once. The first approach leads to duplication of overhead for each core and the need for more complex control mechanisms to coordinate between them. This design goes against the goals of simplicity and efficiency. The second approach, increasing Same Instruction, Multiple Data (SIMD) capabilities for a smaller number of cores requires less overhead to implement and extends the trend started by the growth of Intel's AVX instruction set to include 512 bit wide SIMD capability (Intel, 2021). However, while the amount of circuitry required to perform arithmetic operations on each element scales linearly with the SIMD vector width, the requirements for many data movement operations do not. Thus, algorithms' data movement requirements are the main obstacle in making ultra-wide SIMDs practical.

### 1.2 Proposed approach

This dissertation proposes a solution to this limitation in the context of inference in deep learning. The idea is to show that the flat approach to parallelism is feasible for these applications by implementing deep learning algorithms using the types of local data movement operations that do scale linearly with SIMD width. This approach, called *Memory Movement Minimizing Matrix Math* - *Vectorized Convolution* ( $M^3inM^2VConv$  or MinMVConv) is the main contribution of this dissertation. In this work I will describe the implementation of both convolutional network and recurrent network algorithms on such a novel, ultra-wide SIMD vector hardware architecture.

The target hardware in question, *ncore* by Centaur Technology (Henry et al., 2020), aims to provide enough flexibility to implement a wide range of current and future deep learning algorithms, as will be shown by the implementation of a wide range of such algorithms on an emulator of the hardware. The hardware design attempts to create this flexible platform by way of an ultra-wide SIMD architecture, utilizing simple arithmetic units arranged in a ringlike fashion that allows for some simple data shift operations to be performed with extremely high efficiency. If this architecture were implemented in a form that kept cost and power consumption down it could be deployed in a wider range of commodity devices including small servers, laptops, gaming platforms and perhaps even smaller devices, allowing for the increased use of pretrained networks for things like facial, voice, gesture and/or hand-

writing recognition closer to the "edge". These tools could be applied to a wide range of use cases, from data input and device control to interacting with video games. Furthermore, efficient, widely deployable hardware support for deep learning models would facilitate support for such capabilities without the speed, security and privacy concerns associated with offloading these functions to the cloud.

# 1.3 Real world application: decoding neural signals

Building on the above approach, this dissertation shows that learning algorithms on such hardware provides an advantage in solving practical problems. In addition to consumer applications such a hardware accelerator might be applicable to a range of other scientific and industrial uses, especially if it addresses power consumption concerns. While "traditional" deep learning applications such as computer vision/image processing, audio and speech recognition and text processing have applications in a wide range of domains, one could imagine that other applications of deep learning algorithms could expand this applicability even further.

As an example of a lesser explored application of deep learning I will look at the application of recurrent deep networks to computational neuroscience, specifically the decoding of information encoded in the electrical spiking activity observed from ensembles of biological neurons. Simpler recurrent network models with a limited number of learned parameters have been recently shown to be effective at decoding neural spiking activity (Sussillo et al., 2012). In this work I will show that such meaningful information can be gleaned by gated recurrent networks from a dataset consisting of behaviorally correlated activity of neurons in an auditory processing area of the rat brain (Sloan et al., 2009, Sloan, 2009).

While most of the computational time is spent on training the networks, running such neural decoding algorithms on hardware that is optimized for inference using deep networks is still relevant. Specifically, while much current work on observed neural signals is focused simply on figuring out how the brain encodes information, many researchers hope that someday such decoding of neural signals could be used to drive brain-machine interface and neuro-prosthesis systems (Smith et al., 2013). While most research applications can make use of relatively large compute clusters, simpler hardware with lower power requirements would be better suited for running a controller for a prosthetic device.

One limitation of this approach is that the training stage will not be considered on the proposed hardware architecture. However, the ability to decode neural signals using a trained network running on small and relatively low-power hardware is still an important advancement towards eventual applications in the domain of neural controlled prosthetic devices. Even without training capability such applications would benefit from the fast and potentially low power inference capabilities that could be offered by hardware architectures like the ultra-wide SIMD. Having such highly mobile and low power hardware available when the rest of the scientific and engineering hurdles have been cleared to make such prosthetics a reality, will be the final piece of the puzzle. Furthermore, there are likely many other applications in other domains, where the ability to perform inference using deep learning without the need for large and power hungry hardware will similarly help facilitate the deployment of practical innovations stemming from basic scientific advancement.

The field of neuroscience, along with many modern other biology disciplines, increasingly reliant on machine learning algorithms to not only analyze data, but to build models that can provide clues as to what theories might be fruitful to test experimentally, or what variables to look for in the data. Even old datasets can be reanalyzed with new algorithms that were previously computationally intractable to yield new insights. Thus, given that most researchers' budgets are finite, anything that increases the amount of usable computational power available for that budget increases the ability to analyze data.

#### 1.4 Guide to the reader

The dissertation begins in Chapter 2 with an overview of related work, algorithms and hardware. Then I will provide an in depth description of the proposed hardware that MinMVConv will run on. Chapter 3 follows with the details of the convolution algorithm itself, including some interesting variants. Next, in Chapter 4, the performance of my proposed algorithm is analyzed as a function of the hardware parameters.

In order to provide an example of implementation of MinMVConv on existing, widely available hardware, an AVX-512 implementation is presented in Chapter 5.

My accompanying analysis of this implementation compares the hardware utilization efficiency to that on the proposed class of ultra-wide SIMD architectures for which the geometry-aware convolution algorithm was developed. While the number of data elements contained within a 512b SIMD line is insufficient to fully showcase the strengths of my MinMVConv, the implementation does still show that the algorithm can be implemented and run in real, existing hardware.

In further support of the general utility of algorithms like MinMVConv Chapter 6 addresses the issue of recurrent network layers. While the implementation of even "complex" recurrent layer types, such as LSTMs, is relatively simple. The fact that they can be implemented with an MinMVConv like approach shows that the proposed hardware and programming approach is capable of supporting networks that contain these layers, possibly in combination with convolutional layers.

To demonstrate the practical utility of MinMVConv to a new domain, Chapter 7 discusses the application of convolutional and recurrent deep networks to the emerging area of using deep learning to decode neural signals. While interesting in of itself from a scientific perspective, the proposed MinMVConv algorithm and the simple, ultrawide SIMD architecture that it supports open the door for low power requirement applications of neural decoding, such as the control of prosthetic devices.

#### Chapter 2

# Background

From the first perception model proposed by Rosenblatt (1958), neural networks have evolved into often large modern networks composed of many layers of varying types. These networks have inspired new algorithms and hardware architectures in order to run them, and have found their way into a wide range of applications. In this chapter I will give a brief overview of some of the neural network layer types used in modern deep neural networks. I will then describe some of the algorithms and hardware architecture proposed to train and perform inference on these networks, including a description of the proposed class of new ultra-wide SIMD architectures whose development I was involved with and that my work presented here describes algorithms for. Finally I will describe emerging applications of deep learning to the decoding of information from the spiking activity of real neurons.

# 2.1 Neural nets and deep learning

Starting from the simple perception model, neural network algorithms have evolved to include networks with many layers, and often with diverse topologies among these layers. Here I will briefly discuss this evolution, and then I will describe two of the major topologies that expand on the classical fully connect layer; convolutional networks and recurrent networks.

# 2.1.1 Deep learning and the resurgence of Neural Network Algorithms

While artificial neural network algorithms are much older than the current popularity of "deep learning" several factors have made the training and evaluation of large scale neural networks practical. The first factor is the increase in available computing power. The second factor is related to this, and it is the increase in the amount of training data available in certain domains. This is especially image processing, where the ability to crowd source much of the work in generating a dataset led to the creation of the well known ImageNet dataset (Deng et al., 2009), which then gave rise to successful deep networks such as AlexNet (Krizhevsky et al., 2012). While more ambitious datasets and networks have been developed since, they all share common building blocks in their use of variations on convolutional, or ConvNet layers. Unlike fully connected layers, ConvNets utilize relatively small filters that are then used to perform a 2D convolution with the input. This requires fewer total parameters, and allows the networks to more easily capitalize of the spatial relationships within the input.

Likewise, for domains such as text and speech processing, where temporal information is important, improvements in recurrent network algorithms have made such algorithms practical in more applications. These improvements, which include adding gates to the recurrent units that determine what information is used to determine the unit's output (Hochreiter and Schmidhuber, 1997). These gates help prevent useful information from being lost over larger timestep intervals, and aid in training the networks.

#### **Convolutional Networks**

The first well known use of convolutional networks was the use of the LeNet architecture on the MNIST handwritten digit dataset (LeCun et al., 1998). While much simpler than most modern convolutional network applications this network had all of the building blocks used in those newer networks, including the reuse of weights through the convolution of the same filters with all locations across the input image, and the use of max pooling to reduce the dimensionality of each layer's output.

As an example I will discuss a simplified version of the LeNet network, with fewer layers, that is used as part of the tutorial for the deep learning toolkit Theano Al-Rfou et al. (2016). This network takes as it's input the 28 × 28 images from the MNIST dataset. Unlike the  $224 \times 224 \times 3$  RGB inputs that AlexNet uses from the ImageNet dataset the MNIST inputs have only one channel. This means that while convolutional network filters are generally described as being  $R \times S \times C$  filters where R is the number of rows, S is the number of columns and C is the number of channels the filters for this LeNet variation on the single channel MNIST dataset are  $5 \times 5 \times 1$  filters. There are 20 such filters in the first layer of this network, are they are commonly referred to as *filter groups*.

The term filter groups makes more sense in terms of the second layer of the

network. Here each of the 50 filter groups take a 20 channel input (for a  $5 \times 5$  filter). Each channel is the output of the previous layer. Within a filter group the 2D filter for each channel is convolved with that channel's 2D input by sliding the window across the input and summing the products of the filter coefficients with the "pixels" covered by the filter. The 2D matrices resulting for the convolutions of all channels are then summed to create a single output per filter group.

If same size convolutions are used then the input image is padded with zeros and the output of the convolution for each filter group has the same number of rows and columns as the input. If only the *valid* convolutions are used then the output is slightly smaller than the input, as convolutions where the filter hangs off the edge are not used. In either case, since the outputs of each filter group have roughly the same 2 dimensional size as each input channel the total size of the input to each layer will grow if the layers have more filter groups than input channels. To combat this, and to build some degree of translational invariance into the network a technique known as *max pooling* is used.

In max pooling the final output of each filter groups convolution is divided up into small sectors. In the basic case these sectors are small non-overlapping squares, and in the case of the modified LeNet network example discussed above are  $2 \times 2$ . Out of the convolution results in this square only the largest value is selected as part of the actual output to the full layer. Thus for the LeNet MNIST example, the  $24 \times 24$ output of each filter group of the first convolution is subsampled via max pooling to yield a  $12 \times 12 \times 20$  output across all filter groups in the layer.

#### **Recurrent Networks**

Convolutional layers can be mixed with fully connected layers to form powerful classifiers for inputs that represent a single point in time (or consist of information properly combined over a period of time). They cannot, however, form a representation that includes information about inputs that the network has recently seen, without modifying the weights through training. Recurrent neural networks can accumulate information over time, however. Thus they are natural choices for application where the data is best viewed as a timeseries. Practical applications include speech and text processing, music identification, and even handwriting recognition when sequence of the actual penstrokes is known (Cho et al., 2014, Greff et al., 2015)

The most basic recurrent network layers simply consist of fully connected layers where the outputs are connected back to the units in that layer, as well as being used as inputs to the next layer. However, many modern recurrent layers make use of gating mechanisms to control what gets output from each unit. These gates are sigmoid functions of the inputs (recurrent and non-recurrent) to each unit, or cell. The first such recurrent architecture to be proposed was the Long-Short Term Memory(LSTM) networks proposed by Graves and Schmidhuber (2005).

A LSTM cell contains three gates, along with a cell state. The three gates, know as the input(i), forget(f) and out(o) gates are computed as follows, where  $\sigma$  is the standard sigmoid function, with a range between zero and one:

$$i = \sigma(W_i * x_t + U_i * h_{t-1} + w_{ci} * c_{t-1} + b_i)$$

(2.1)

$$f = \sigma(W_f * x_t + U_f * h_{t-1} + w_{cf} * c_{t-1} + b_f)$$

(2.2)

$$o = \sigma(W_o * x_t + U_o * h_{t-1} + w_{co} * c_t + b_o)$$

(2.3)

The W \* x and  $U * h_{t-1}$  terms are vector multiplications between the weights and in incoming and recurrent connections respectively. The w \* c terms are scalar multiplications that are used to include the cell state in the calculation of the gate values themselves. These connections are known as *peephole* connections, and some or all are left out of some LSTM variants. It should be noted that if peephole connections are used the outgate (Eq. 6.3) uses the cell state for that timestep. The input and forget gets, which are used to calculate the cell state, get their peephole connections from the cell state at the previous timestep.

The new cell state is computed using the input and forget gates as follows, where the input gate controls the contribution of the incoming and recurrent connections to the new state, while the forget get determines the contribution of the previous timestep's cell state:

$$c_t = i * tanh(W_c * x_t + U_c * h_{t-1} + b_c) + f * c_{t-1}$$

(2.4)

The cell's actual output is then determined by taking the tanh of the state and

scaling it by the output gate:

$$h_t = o * tanh(c_t) \tag{2.5}$$

While LSTM networks have proven effective on a wide range of tasks, the model is complex, and each gate adds a potentially large number of parameters to train. This is especially true as the number of cells in a layer increases, as the number of recurrent connections is  $N^2$ , where N is the number of cells in the layer. A newer type of gated recurrent layer, known as Gated Recurrent Units (GRUs) reduces the number of parameters by reducing the number of gates by one, and eliminating the cell state (Cho et al., 2014).

The remaining two gates in the GRU model are known as the update(z) and reset(r) gates, and are computed as follows:

$$z_t = \sigma(W_z * x_t + U_z * h_{t-1} + b_z)$$

(2.6)

$$r_t = \sigma(W_r * x_t + U_r * h_{t-1} + b_r) \tag{2.7}$$

Like the LSTM cells, the *tanh* function is then used in the calculation of the cell output, however the GRU cell determines it's output directly from the gates and the previous output, with no need to maintain a separate state value:

$$h_t = z * h_{t-1} + (1-z) * tanh(W_h * x_t + r * (U * h_{t-1}) + b_h)$$

(2.8)

It should be noted that the  $z * h_{t-1}$  term is a scalar multiplication between the update gate and the previous timestep's output for *that* cell, while the  $U * h_{t-1}$  term is the dot product between the recurrent portion of the weight matrix and the previous timestep's output from all cells in the layer. Thus the intuition behind the update and reset gates is that the update gate determines how much the previous timestep's output for the cell determines the new output directly, compared to the influence of the connections coming into the cell. The reset gate on the other hand determines how much influence the recurrent connections have on the incoming connections' part of the output.

#### 2.2 Computing hardware and deep learning

While, historically limitations created by contemporary compute hardware hindered the development of neural network algorithms, in recent years neural networks and deep learning have driven the development of algorithms and even new hardware architectures to facilitate more efficient training and evaluation of neural networks. This includes both efforts to simply speed up the matrix/vector multiplication inherent in evaluating all neural network layers, especially fully connected and recurrent layers, and algorithms and hardware to specifically speed on convolutional layers. It is convolutional layers that I will focus on most specifically here, but with respect to algorithms for their evaluation on standard CPU and GPU hardware, and on hardware architectures designs specifically for neural network computations.

# 2.2.1 Implementation of Convolutional Networks across Hardware Architectures

Due to their popularity and use is a wide array of research and production applications, many optimized implementations of ConvNets have been developed for different architectures, including standard x86 CPUs, GPUs and other prototype hardware architectures. Many of these implementations are part of deep learning tools such as Theano/Lasagne (Al-Rfou et al., 2016), Caffe, or TensorFlow. These tools often break up networks into modular layers, such as a convolution layer or a recurrent layers. Layers of a specific type have meta-parameters for their size, training options etc, and allow for the architecture of the network itself to be specified with limited consideration for the actual implementation or even the hardware it will be run on. It is the implementation however, that I am concerned about in the first part of my work. Here I will discuss implementations that others have developed, for x86 based CPU architectures, GPU architectures and novel, deep learning specific hardware.

#### 2.2.2 x86 Implementations

The most naive approach to implementing a convolutional or recurrent network is to simply calculate the output to each layer serially, performing single multiply-add operations between each weight and the appropriate input value(s). While this might yield code that is easy to understand and debug, it does not take full advantage of the capabilities of modern CPUs. Even if the work were parceled out such that each core is performing calculations, the SIMD capabilities of the cores are ignored, with only one multiply-add operation be performed at once as opposed to the eight to 16 such single precision floating point operations that can be performed simultaneously on many modern Intel CPUs (Intel, 2021). Common compilers, including Intel's C/C++ compilers and the open source gcc and g++ compilers, have optimization options that can attempt to allow code to automatically make use of these SIMD capabilities, and many libraries exist with optimization implementations of common mathematical operations.

For a fully connected neural network layer it is simple to take advantage of this SIMD capability, through the use of these optimized libraries. Assuming that the weights are arranged properly the bulk of the computational load can be performed as a simple matrix dot product, with an element wise addition for the bias terms. These are both operations for which there are many well optimized libraries to perform, such as the well known BLAS library. The connectivity of more complex network layer times is not this simple, however any many cases it can still be transformed into a matrix operation. Likewise, the primary computations for simple fully connected recurrent layers can be broken up into the sum of two dot products, one for the layer input, and the other for the recurrent connections. For gated recurrent networks the bulk of the computation comes from multiplying the values from the incoming and recurrent connections to compute the values for the gates and cell state or output. In the case of an LSTM layer, this means calculating the product of the same incoming and recurrent inputs with weights for the in, forget and out gates along with the cell state (Hochreiter and Schmidhuber, 1997). All of these values can be computed at once using a similar sum of dot products strategy.

Unlike many basic and recurrent neural network layer types, one key feature of convolutional networks is that they are not fully connected (LeCun et al., 1998). This however means that more complex manipulations are required to formulate the layer's computations in a way such that they can be carried out using a small number of standard matrix computations. One such method is proposed by Chellapilla et al. (2006). This method duplicates the input values to create a matrix where each row contains all of the values needed to compute a given output. The weight values are then arranged appropriately, with no duplication, to allow the majority of the computations needed to compute the layer output to be performed as part of a single dot product.

### 2.2.3 GPU implementations

While the matrix method of performing convolutions can was developed to take advantage of optimized matrix multiplication libraries and SIMD capabilities of modern CPUs the same method can also be used on GPUs. One such implementation is cuDNN (Chetlur et al., 2014). Another method developed for implementing large convolutional networks on GPUs involves the use of an Fast-Fourier Transform (FFT) (Mathieu et al., 2013). The FFT transform is used to transform a layer's filters and inputs from 2d spatial images to the frequency domain, where the the actual convolution operation can be performed with a single step. Like the duplication of data in the matrix method, the FFT transform incurs extra overhead, however since the transformed values can be reused the overhead is made worthwhile by the savings in computational operations across all computations performed.

# 2.2.4 Custom and experimental hardware implementations

Besides optimized CPU and GPU implementations, a third route for implementing neural network algorithms is to use hardware that was designed primarily for running neural network algorithms. While still much less flexible in their capabilities than a modern CPU or GPU some of this architectures have been designed for the general types of calculations performed as part of neural network algorithms, and posses the flexibility to implement a wide range of neural network algorithms.

In their DianNao architecture, Chen et al. (2014) focus on such an approach, implementing a SIMD architecture that is designed with the memory locality structure of convolutional networks in mind, maximizing the usage of data elements that have been fetched from RAM. They take advantage of the structure of input (x,y, channel) and of the 2D convolution to inform arrangement of data in memory and order of operations and accomplish this by having a circular input buffer that feeds the data to the SIMD unit. This buffer is filled with input values from different channels but the same x, y location, and all calculations that need this values are accomplished and stored in another buffer before the initial set of inputs are replaced with a new one. Their hardware design is somewhat unusual, however, in that it broadcasts the input channels the 16 inputs that it can handle at once to all 16 arithmetic units, while the 16<sup>2</sup> total weight values read in together are divided up among the arithmetic units. The focus behind this scheme is memory reuse. It achieves reuse of the data values, as multiple partial calculations that use the same X,Y locations are completed before that data is removed from the buffer nd replaced with new data. The temporary storage registers for the partial sums do add additional complexity to the hardware however, and the number of such buffers places an upper limit on the number of partial sums that can be stored, and by extension limits data reuse.

A successor architecture to DianNao, Cambricon (Liu et al., 2016), addresses some of the flexibility concerns of DianNao by implementing more general matrix operation primitives. However, both proposed architectures are limited in the width of their SIMD capability and would likely not scale well. This means that a higher clock speed would be required to get the same throughput as more highly parallel methods.

Another novel design, proposed by Han et al. (2016), focuses specifically on accelerating deep networks with sparse weights. This proposed architecture, the Efficient Inference Engine, consists of many, relatively small SIMD compute units. The authors claim improvements in inference speed and power consumption compared to CPU or GPU based inference algorithms. However, this speed and efficiency is achieved by putting strict requirements on the sparsity of both the data and the weights, and by constraining the final weight values of the network to belong to a small set of discrete values. While this might work for some networks and result in a very efficient hardware design for certain situations it is unlikely to work for all networks, limiting the architecture's usefulness as a general deep learning inference engine.

#### 2.2.5 TPUs

Another major hardware architecture that should be mentioned is Google's Tensor Processing Unit (TPU), as it has seen production use as a data center based device designed for neural network inference. The TPU utilizes pipelined CISC instructions that allow for many clock cycles to by spent in each pipeline stage. Additionally, the pipeline is designed such that data movement operations and auxiliary post-processing operations can be performed simultaneously with the main fused-multiply-add (FMA) workload, preventing these background operations from delaying the arithmetic operations that need their results whenever possible (Jouppi et al., 2017).

The primary arithmetic operations are either  $8b \times 8b$ ,  $8b \times 16b$ , or  $16b \times 16b$  integer multiplies added to a 32b accumulator, with wider operations taking multiple clock cycles. The FMAs are performed in chunks of 256 elements at a time inside a  $256 \times 256$ systolic array *Matrix Multiply Unit*, and once they leave the Matrix Multiply Unit the accumulators' values can be stored for later or sent to a separate hardware unit that handles activation functions and similar post-processing operations (Jouppi et al., 2017). While custom ASICs could previously be tailored to a specific neural network workload, the TPU's neural network specific design secures is a first as a drop in, neural network specific hardware solution for use in production systems.

#### 2.3 AVX-512 Overview

However, just because solutions exist that are specifically targeted for neural network inference exist doesn't mean that general purpose hardware shouldn't be considered - especially since most neural networks are part of a bigger system made up of more general code. Thus, the final SIMD paradigm that deserves more through discussion is Intel's AVX-512 instruction set, as it is built in to many modern high end Intel server and consumer grade CPUs (Intel, 2019), and has many open source libraries that take advantage of it, including tensorflow (Abadi et al., 2015). unlike the previously mentioned architectures, the AVX-512 instruction set was not built with neural network workloads specifically in mind, but instead builds on a history of SIMD technology developed for Intel x86 CPUs for multimedia, communication and general purpose SIMD operations. This history begins with the MMX instruction set extensions introduced on Pentium II CPUs, which provided integer operations on a 64b vector width, mostly targeted at multimedia and internet communications applications. Later improvements to SIMD functionality came with the Streaming SIMD Extensions (SSE) which introduced 128b wide SIMD vectors along with floating point support. This expanded vector width then grew to 256b with the introduction of Advanced Vector Extension (AVX and AVX2) instructions, which also introduce fused multiply-add capability which is commonly used in neural network applications (Intel, 2021). Finally, the AVX-512 instruction set increased the SIMD vector width to 512b, being released initially as a specialized many-core compute device in the first generation of Xeon Phi, known as *Knight's Landing*. AVX-512 was brought to standard CPUs designs with the Skylake-X consumer focused line, and as of 2022 can now be found in most recent Intel Core (consumer market) and Xeon Scalable (server) CPUs, although it's not available on the latest 12th generation "Core" CPUs (Intel, 2019).

#### 2.3.1 Changes from previous AVX instructions

The most obvious change between AVX-512 and previous AVX instructions is the increase in SIMD width. However, AVX-512 also follows the trend of increasing register space for SIMD instruction with each generation of SIMD capability. Specifically, while MMX instructions introduced only 8 64b SIMD registers, the SSE instructions increased this to eight larger 128b xmm registers could be split into 16 64b for SSE/SSE2 instructions. The original AVX instructions introduced the 16 256b ymm registers, which doubled in both number and size for 32~512b wide zmm registers used for AVX-512 instructions (Intel, 2021). This increased register width allows for a greater amount of data to be kept immediately available for use. Additionally, while previous SIMD instruction sets have had a few iterations (e.g. SSE, SSE2, etc), AVX-512 consists of multiple groups of instructions in addition to the original "Foundation" instructions (AVX-512F) (Intel, 2021). While it is possible to detect which of these instruction groups are supported on a given CPU, this ambiguity as to what constitutes AVX-512 makes generalized development more difficult, especially since some the instruction groups include things like 16b floating point support that are potentially useful for neural network applications (Intel, 2021).

# 2.4 Ultra-wide SIMD hardware description

Finally, I will describe the proposed ultra-wide SIMD architecture for which the algorithms described in this document were developed. This proposed architecture, known as *ncore*, trades off the ability to perform a wider array of data movement operations such as those available in AVX-512 for the ability to do as many simple arithmetic operations at once as possible, with SIMD widths an order of magnitude wider than the TPU. This section describes this hardware design and the philosophy

behind it.

#### 2.4.1 New Ultra-wide SIMD Hardware

Relatively narrow SIMD operations, such as the 128, 256 and 512*b* wide SIMD operations provided by current or upcoming x86 ISAs provide a larger amount of flexibility in their use, since they operate on a relatively small amount of data at once, compared to the size of many matrix operations used in deep learning applications. Architectures with a higher degree of parallelism offer the opportunity to complete a larger chunk of a matrix operation within a single instruction. New implementations of deep learning primitives however are likely needed in order to take advantage of of the greater parallelism offered by such a new architecture. Here I will describe one such proposed ultra-wide SIMD architecture, in order that I can define new methods to use the architecture for deep learning calculations. The hardware was developed by a team that I worked with at Centaur Technology in Austin, TX, and is the hardware for which I will develop implementations of convolutional and recurrent deep network algorithms. In order to aid in the understanding of my implementations I will first describe the basic functionality and unique aspects of the hardware on which it will be run.

### 2.4.2 Hardware and Instruction Set Architecture (ISA) Overview

The primary building block of this proposed hardware architecture is a hardware "slice" concept outlined by Henry (2020), consisting of memory, a Neural Data Unit (NDU), a computational unit (Neural Processing Unit (NPU)) that can take two input values and perform at least the limited set of arithmetic operations needed for common neural network architectures, including a large number of multiply accumulates, and a output/post-processing unit. These are arranged to form a deterministic pipeline, where each stage feeds the next while allowing data movement and post-processing operations to take place simultaneously with the basic addition and multiply operations that make up the bulk of neural network computations.

The main pipeline begins with the data movement stage, the NDU, that controls the NPU inputs, allowing for inputs from memory registers, previous outputs, and operations that allow the previous operation's input(s) to a unit to be be sent to an adjacent unit at a given distance and direction within a relatively smaller number of SIMD units, either as a rotate, local broadcast, or similar operation. This movement capability essentially makes a logical ring out of the processing units, facilitating local data movement without the overhead of large scatter/gather operations, but still allowing data to (eventually) reach any location across the SIMD width using a sequence of rotations, but without changing the relative order of the data elements.

The data movement stage feeds the NPUs, where each computational unit includes an arithmetic unit that performs FMAs and related operations, and an "accumulator" register that is used to store the intermediate results of such sequences of simple operations. The result of a string of these arithmetic unit operations can then be sent to an Output/Activation unit, similar to that in the TPU, where a provided function (e.g. tanh) or other post-processing step can be applied to the accumulator value before it is either be written back to memory, or used as input to further arithmetic operations.

This simplest such network layer that one can evaluate on this architecture is a fully connected layer whose input and output sizes are less than or equal to the SIMD width. Using this architecture the output of a single such layer can be computed as follows:

- 1. The input to the network along with the first row of the weight matrix are loaded from cache/memory.

- 2. Prior to performing any calculations the accumulator registers of all computational units are set to zero.

- 3. Element-wise multiplication is performed between the network input vector and the first row of the weight matrix, and the result added to the computational units' accumulator registers.

- 4. The values from the input vector are then shifted, such that the value that was used by computational unit i for the last multiply-accumulate operation is transferred from the input register of unit i to computational unit i + 1. This value is then used as an input to the next element-wise multiply-accumulate operation, along a new row of weights fetched from memory.

- 5. This process is repeated until all elements in the input vector have been provided

to each computational unit along with the appropriate weight values. At this point the accumulator register of each computational unit holds the weighted sum of the inputs one of the layer's neurons.

- 6. The bias value is then added to each computational unit's accumulator register as a single SIMD operation.

- 7. The appropriate activation function is applied to the contents of each computational unit's accumulator register, and the result written back to memory.

In fully connected layers where there are more inputs to the layer than can be fit across a single SIMD row the additional inputs can be placed in another row. Steps three through five are then repeated for each SIMD row of input data. Likewise, layers that have more neurons in them than computational units in the hardware can be computed be repeating the whole process M times, where  $M = \frac{ceiling(layer_{size})}{computational_{units}}$ .

While the above example uses the values in the computational units' accumulator registers to write the layer output back to memory, as state previously, the capability to use a function of these registers' contents directly as an input back into the computational units is also provided. This functionality is important for efficiently implementing recurrent neural networks. To further facilitate the implementation of gated recurrent networks limited ability use the computational units' output as input to adjacent computational units is also provided.

### 2.4.3 Motivation for Ultra-wide Paradigm

While the high-level goal driving the design of ncore was performance per total system cost due to its nature as a on-die co-processor, the low-level design was driven by multiply-accumulate (MAC) efficiency, and design scalability (Henry, 2020). Specifically, multiply-accumulate (MAC) efficiency meant that both the hardware and software algorithms were designed to maximize the usage of the main arithmetic units each clock cycle, whether fused multiply-add (FMA) operation, or other simple arithmetic operations that could reuse most of the hardware components of the FMA units. The repetition of this simple hardware design in the slice concept described above allows for groups of identical arithmetic units along with their supporting data movement and output functions to be repeated across the SIMD width as a larger hardware module, simplifying the hardware design process and allowing the SIMD width to be changed by simply changing the number of these modules.

While at a high-level ncore's pipeline is similar to the TPU, this design highlights a major difference in low-level design. Namely, the organization of ncore around a simple, repeated "slice" reduces the size of the hardware design problem, simplifying the process of design and testing, allowing for a new version of the hardware to be easily designed with a different SIMD width as dictated or allowed by hardware technology or application requirements, and potentially allowing more compute units on the same physical chip by facilitating optimization. Plus, some would argue that such simpler design paradigms are less vulnerable to the ever increasing scourge of security vulnerabilities (Henry, 2021).

# 2.5 Machine Learning and Decoding Neural Signals

The reason that so many hardware solutions have been developed for neural network training and/or inference is that these algorithms have proven themselves useful in a large array of fields. Well known examples include computer vision and speech processing, but neural network algorithms can be used many fields where sensor data or other similarly large volume input needs to be interpreted or have a label assigned to it. One such field is computational neuroscience and the interpretation of observed neural signals.

Neuroscience researchers utilize a wide range of methods for observing, either directly or indirectly, the activity of neurons. These methods range from invasive methods for directly observing the activity of small numbers of individual neurons in animal studies, to non-invasive methods, such as fMRI or EEG, that allow for the observation of the entire human brain, albeit at a much coarser temporal and/or spatial scale. The types of data generated by these observations varies. However, almost all methods yield large amounts of data whose interpretation often requires powerful analysis tools.

# 2.5.1 Machine Learning Techniques for Neuroscience Timeseries Data

Some such analysis methods focus on inferring other aspects of the data such as structure, as in (Huth et al., 2015) for example. However, here I will focus on situations where some form of classification or regression is performed on the data, often to infer something about the stimulus that drove the observed neural activity, or the behavior(s) of the organism that that resulted from it. My primary focus will be on the challenges of inferring the information encoded in spikes observed from individual or groups of neurons. However, I will also discuss techniques used for other modalities of neural data, as most such methods share the challenge of extracting meaningful information from a noisy and incomplete observation of the brain.

# 2.5.2 Simple Classifiers

Perhaps the simplest method of quantifying the relationship between the spikes observed from a neuron or group of neurons in correlation to a stimulus that has been presented to the system is to simply count the number of spikes within a specific time period after a given stimulus is presented. These spike totals can be collected for a single neuron repeatedly as some parameter of the stimulus is varied. For example Hubel and Wiesel (1962) used simple bars of varying angles to map the receptive fields of cells in the cat visual cortex.

While this spike counting approach is extremely simple, counting spikes over a long period relies on the assumption that any information encoded by changes in spiking within that period is not relevant. Foffani and Moxon (2004) expand this concept to build a histogram of observed spikes over multiple time bins during and shortly after the period in which a given stimulus is input into the system. These histograms can then be used to create a simple classifier that can infer which a stimulus label for a new histogram of spikes. A smooth version of a PSTH histogram can also be created by convolving a Gaussian kernel with a vector called a *spike train*, which contains a one at all points in time where a neuron was observed to be active, and a zero at all other locations. While this method, similar to that employed by Smith et al. (2013) in their analysis of neural responses in the primate auditory system, helps remove noise from the signal of observed neural activity further processing is needed to be ability to decode or quantify information about the stimulus that drove the observed neural activity.

# 2.5.3 Machine Learning

Smith et al. (2013) use principal component analysis to reduce the dimensionality of their histograms of neural activity and then use a linear discriminate analysis (LDA) classifier to decode the stimulus that drove the activity. Similarly, Support Vector Machines have been used to expand the categorical classifier into a multidimensional space.

#### 2.5.4 Neural Network Algorithms

Besides direct classification on the observed data, machine learning tools that build a lower dimensional representation of their input can also be used to transform the stimulus thought to have evoked observed neural activity input a form that can more easily be related to that activity. For example, Agrawal et al. (2014) utilize convolutional neural networks to predict voxel intensities for fMRI data for vision related brain regions ranging from V1 to higher level visual areas. They do this by presenting the stimulus images used in the fMRI study to a ConvNet trained on the ImageNet dataset. A feature vector can then be extracted from the intermediate layers of the network that can be used to predict the observed voxel intensities using a simple regression method.

Modern deep learning methods developed as machine learning tools are far from being faithful models of real neurons. However, their simplified nature makes them tractable models of the brain that still can be valuable in some cases. One obvious area where deep learning networks designed for machine learning problems might still be helpful for modeling the brain is for low level vision. One surprising property of even early deep convolutional networks trained on natural images is their tendency to learn filters in their initial layers that resemble the receptive fields of cells in the primary visual cortex (V1). Furthermore, Lee et al. (2007) show that higher layers of some deep networks can learn filter basis functions that resemble receptive fields found in a subsequent layer of the visual cortex (V2).

It is this tendency to learn representations at lower network levels that are sim-

ilar to known receptive fields at lower levels of sensory processing in the brain that make them good candidates for generating feature vectors and representation for applications such as that of Agrawal et al. (2014). Furthermore, this tendency of deep networks to mimic the known receptive fields of actual cells in the brain extends beyond convolutional networks and the visual system. For example, Kanitscheider and Fiete (2016) use LSTM networks as a model of areas of the hippocampus used for navigation. Similar to computer vision networks trained on object recognition from input image, these recurrent networks are trained to predict location in a simulated environment using inputs similar to those believed to feed into regions of the hippocampus responsible for navigation tasks. The recurrent cells in the hidden layers networks display a tendency to learn "receptive fields" similar to those observed in actual cells in the hippocampus.

The task of decoding observed neural activity related to a sensory task in the brain is different from using a classifier to perform a similar task. However if you consider sensory processing in the brain to be a phenomenon that occurs in stages from input to decision or behavior, then decoding neural activity observed at an intermediate stage can be thought of as designing a classifier to mimic the functionality of subsequent stages. Such a classifier need not necessarily process the the information in the same manner as these later stages of processing in the brain. However, the fact that deep networks tend to learn similar representations to those in the brain, with the representations at subsequent deep network layers resembling subsequent known stages over sensory processing, makes these networks a good candidate for mimics the function of the later stages for such decoding applications.

#### 2.5.5 Timeseries Algorithms for Neural Data

Some modalities of neural data, such as the fMRI study discussed above, have low temporal resolution. In such cases algorithms that take temporal information into account are less likely to be useful. However, other modalities of measuring activity in the brain, such as EEG or MEG, or the observation of the actual spiking activity from individual cells, has very high temporal resolution. In the case of data from such an observation modality, using models or algorithms that take into account time and/or frequency, which describes the variation of a signal over time might be more useful. Buzsaki (2006) mentions the dichotomy between time and frequency domain measures of a signal, and compares the analysis of neural timeseries to the analysis for speech or other acoustic timeseries where information from both the time and frequency domains are important. LSTMs address time directly, frequency less so, but speech and music processing are common applications of recurrent neural networks (Greff et al., 2015), showing their potential to handle such information. Furthermore, LSTMs have been applied to decoding attention or emotion information from EEG data (Soleymani et al., 2014). This shows that not is the application of LSTMs to EEG data feasible, but that at least in some cases problems such as noisy training sets of limited size are not barriers to the use of recurrent deep learning algorithms.

#### Chapter 3

# Convolutional Network Computations on Ultra-wide SIMD Hardware

Many algorithms already exist for implementing convolutional network layers on GPU hardware, or traditional CPU SIMD architectures. However, due to the unique features and limitations of the previously described ultra-wide SIMD hardware, I have implemented a new algorithm to compute the output of a convolutional network layer that capitalizes on the strengths of this architecture and avoids its weaknesses. It should be noted that this algorithm is only concerned with the forward pass through the layer. However, it could be used as part of a training algorithm, with additional steps to perform the backwards weight update step which would involve more traditional CPU instructions. However, the main goal of the algorithm is to facilitate fast inference on new data by a previously trained network.

In the following sections I will describe how the input data and weight values are laid out in memory to be used by the algorithm. Then I will describe the algorithm itself, along with some extensions and modifications to maximize its efficiency across a wide variety of network sizes and variations on the standard convolution algorithm.

### 3.1 Insight

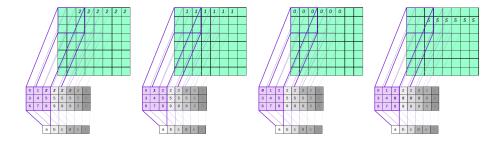

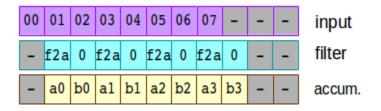

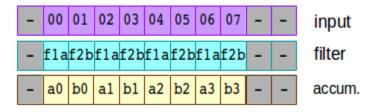

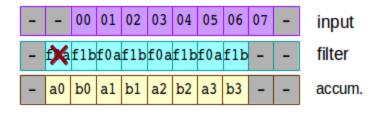

By its nature, convolution is a spatially local operation - to generate each output a few filter coefficients are convolved with a few, adjacent elements of the input. Moreover, spatially adjacent outputs have similarly adjacent input windows in all dimensions. Thus, if the data is arranged correctly, convolution can be performed using only (relatively) local movements of data within a SIMD row. This design facilitates the implementation of an efficient convolution operation on SIMD hardware that does not support scatter/gather operations across the full length of the row.

For convolution with a single channel of input this algorithm is straightforward. Assuming the ability to shift data right by one element within the SIMD row, a row of the input tensor begins lined up with the element of the output row for which they are the rightmost input. These values are then multiplied by the rightmost filter coefficient for the first row of the filter and the input rotated right for the next filter element until the first row of the convolution is complete. This process is then repeated with new inputs for each horizontal row of the convolution filter.

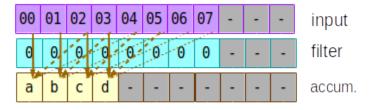

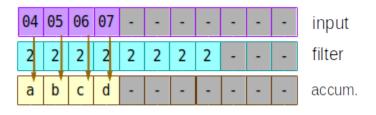

In practice however, deep learning convolution operation neither involves one channel of input, or is the input normally even close to filling the element width of the proposed SIMD architecture. This observation about the data leads to the second main insight of my algorithm: the division of the SIMD row into equal width blocks. The input tensor is then flattened such that row n and channel a of the input tensor is initially placed in the first block of the input row, channel b of row n in the second block, and so forth. This design differs from simply flattening the input matrix in the row and then channel dimension, in that a small number of pad elements may be inserted between each channel in order to maintain even number of equal size blocks across the SIMD row, and allows for a slightly larger, but still local relative to the total SIMD width, rotation to be used to line each block of input up with a new combination of output elements.

Thus, by preserving the original geometry of the each input data, but packing the rows of each channel to maximize the amount of data stored in each SIMD row, convolution can be performed efficiently while performing only local data movement operations within the rows. This allows the algorithm to be run on hardware that does not support global scatter/gather type data movement, or where such operations are inefficient.

# 3.2 Algorithm

The insights outlined above provide the framework for describing both a novel algorithm, known as  $M^3inM^2VConv$ , for performing a multi-channel convolution on the ultra-wide SIMD hardware in question, as well as a data format to facilitate this algorithm. Since the algorithm requires that the data be in a specific, Geometry-preserving layout, I will describe this layout before describing the algorithm itself. Also included in the description of the layout are methods for padding the data to address the fact that unless a network was designed with performance on the particular hardware in mind, it will likely not fit perfectly within the hardware's SIMD width.

Once I have established the required data layout I will describe the algorithm itself. Once I describe its canonical form I will explore the modifications required to support several variations on a standard multi-channel convolution algorithm. These variations include depthwise, strided and dilated convolutions.

### 3.2.1 Layout of input data in cache memory

Unlike the matrix multiplication method for computing the output of a convolutional neural network layer on SIMD hardware that was proposed by Chellapilla et al. (2006), my method does not duplicate the layer's data input values. Instead, I leave the inputs in their original 2D form, with each row of the input occupying a different SIMD row. While these SIMD rows could be laid out in physical memory in any manner that makes sense for the hardware, it is helpful to think of these SIMD blocks as being laid out in a matrix whose number of columns is equal to the SIMD width and whose number of rows is equal to the number of SIMD blocks that can be fit in the cache or other memory allocated to the network. Visualizing the memory in this way, the input values to a layer are laid out in memory in the same manner as they would be if they were pixel values in an image being displayed on the screen.

Unfortunately, the width of the inputs to most ConvNets layers is less than the SIMD width of the proposed hardware (for example AlexNet, a successful ConvNet model utilizing the ImageNet dataset, takes three channels of  $224 \times 224$  input (Krizhevsky et al., 2012)). Obviously if you had a SIMD width of 512, or even greater, it would be inefficient to use an entire SIMD row for each row of a single channel's input.

To address this issue I introduce the concept of a block, which I rely on heavily in my convolutional network layer algorithm, Specifically, to allow for the utilization of memory elements across the entire SIMD width the memory words are divided up into blocks, where the width of a block is the smallest power of two that is wide enough to fit the input width. For example, for a 224 pixel wide input and a 512 word wide SIMD row two blocks of width 256 can be used, though some padding elements are still required if the input width is not exactly a power of two. In the case of the input of width 224, 256 - 224 = 32 pad elements would be needed within each block. Thus, in this case one 512-element-wide memory row could hold one row of the red and green input channels of an ImageNet example. In the most basic version of this scheme the corresponding input row from the blue channel would then be stored in its own memory row, where only one of the two 256 word blocks are used. If hardware's SIMD width were wider, say 1024 elements, then all three channels would fit across one set of SIMD rows, with a 4th block of 256 elements that would remain unused,

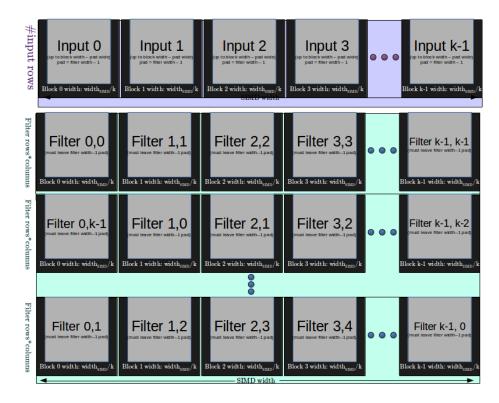

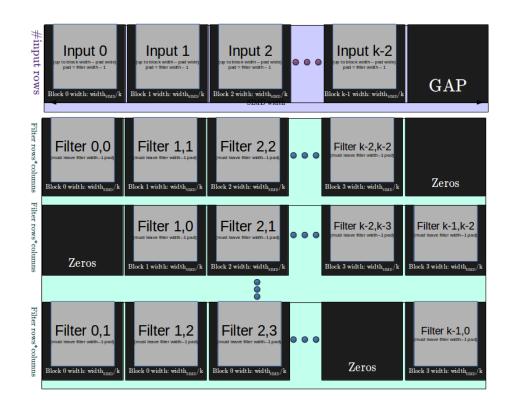

In general, if the SIMD row is divided into k blocks based on the width of the input to the layer then the input data from up to k channels from that layer can be fit in h memory rows, where h is the height of the layer's input. This principle is illustrated in the top row of blocks in Figure 3.1, highlighted in purple.